资质荣誉

热门文章

- 英语课代表趴下让我桶

- 13英寸笔记本评测

- OBOO鸥柏丨100寸飞腾D3000触摸屏多点触控教育学习管理机关会议屏

- 固态硬盘最新资讯-快科技--科技改动未来

- 云意电气:公司以智能电源控制器中心技能为原点推进事务延伸拓宽

联系我们

资质荣誉

TTL电路输入正确接线图

- 发布时间:2024-02-21

- 作者: 资质荣誉

-晶体管逻辑电路,是一种根据双极结型晶体管(BJT)的数字逻辑电路技能。TTL电路因其高速、中小规划集成度和比较来说较低的本钱而大范围的应用于数字体系和计算机

跟着半导体技能的开展,TTL电路现已阅历了多代产品的迭代,从开始的TTL到低功耗的LTTL,再到高速的STTL,每一代都在功能和功耗方面做了优化。

TTL电路的根底原理是建立在两个晶体管组成的开关电路上。输入端接纳电压信号,经过一个NPN型晶体管传递到输出端的另一个PNP型晶体管,终究输出必定的电压水平,表明逻辑“1”或“0”。

当输入为高电平时,即逻辑“1”,NPN晶体管导通,使得PNP晶体管的基极电压下降,然后PNP晶体管截止,输出为高电平。

反之,当输入为低电平时,即逻辑“0”,NPN晶体管截止,PNP晶体管导通,输出为低电平。这种规划使得TTL电路具有快速响应和较强的驱动才能。

1.电源电压:TTL电路常常要5V的直流电源供电。电源的稳定性对电路的功能至关重要。

2.输入阈值:TTL电路的输入阈值大约在1.4V左右,高于这个阈值的输入被认为是逻辑“1”,低于这个阈值的输入被认为是逻辑“0”。

3.输出电平:TTL电路的输出电平通常在3.5V以上为逻辑“1”,在1.5V以下为逻辑“0”。

4.扇出才能:这是指TTL电路能够驱动的标准负载数量。扇出才能取决于电路的规划和负载电容。

5.速度与功耗:TTL电路的速度和功耗是规划中需求平衡的两个要素。高速的TTL电路往往功耗较大,而低功耗的TTL电路速度较慢。

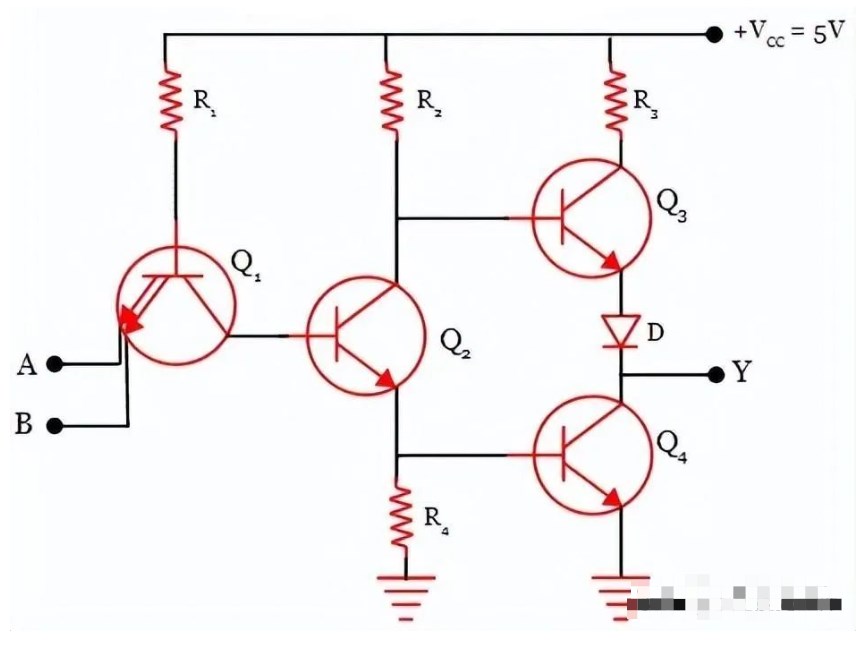

下图为2输入TTL与非门的电路图。它有四个晶体管Q 1、Q 2、Q 3和Q 4。

在发射极侧有两个输入端。三极管Q 3和Q 4组成输出端,称为图腾柱输出。

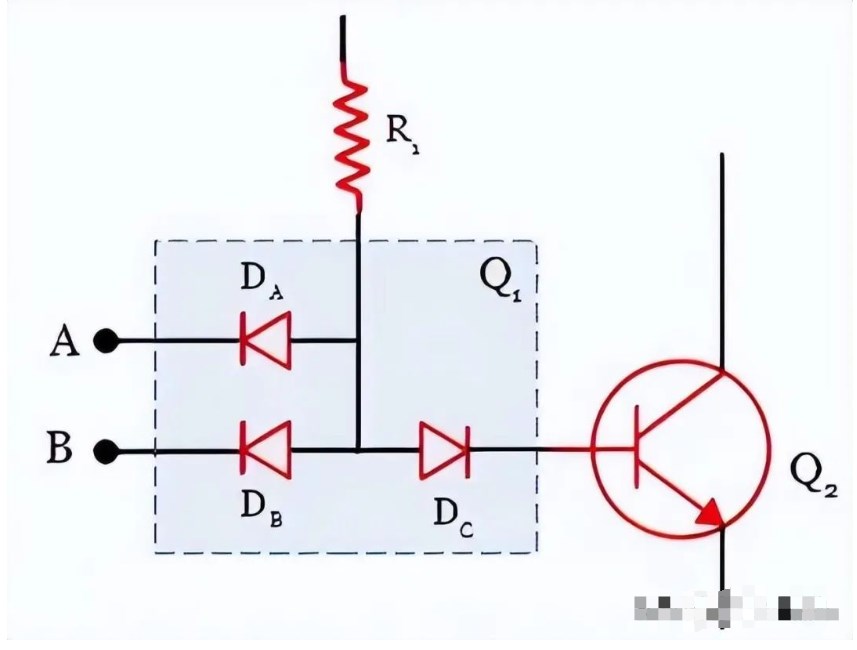

2 输入 TTL 与非门的电路或许看上去很杂乱。咱们我们能够经过考虑 2 输入 NPN 晶体管的

DC代表晶体管 Q2的集电极-基极结。当输入 A 和 B 均为低电平时,两个二极管均正向偏置。因而,因为电源电压 +V CC = 5 V 而产生的电流将经过 R 1 和两个二极管 D A 和 D B 流向地上。

电源电压在电阻R 1中下降 ,不足以导通晶体管 Q 2。跟着 Q 2翻开,晶体管 Q 4也将截止。可是晶体管Q 3被拉高。因为 Q 3是射极跟从器,因而

的输出也将为高电平,即逻辑 1。当任何一个输入(A 或 B)为低时,具有低输入的二极管将正向偏置。将产生与上述相同的操作,在这种情况下,输出将为高电平。

当输入 A 和 B 均为高电平时,发射极-基极结处的两个二极管都将反向偏置。集电极-基极结处的二极管 D C正向偏置。它将翻开晶体管 Q 2。跟着Q 2导通,晶体管Q 4也将导通。输出端的两个晶体管都将导通,因而终端输出将具有低电平,这被视为

声明:本文内容及配图由入驻作者编撰或许入驻协作网站授权转载。文章观念仅代表作者自己,不代表电子发烧友网态度。文章及其配图仅供工程师学习之用,如有内容侵权或许其他违规问题,请联络本站处理。告发投诉

,检查DWG格局的文件需求专用软件,当用AUTOCAD翻开图纸,弹出对话框提示找不到字体时,主张一般挑选hztxt.shx替代。

上灯具;另一种不标准做法:两个开关的动触点上都接入同一回路的相,零线,两个静触点上的出线都到灯具。双联双控开关

的方向吗? 我找到了连接到 Arduino 的阐明,但很难将其转换为我的设备。

STM32F407ZGT6 spi flash片选引脚无法被拉低的原因?怎样处理?

讨教:在运用UDE STK时,单片机运用SPC560D30L1,在配置文件怎样设置或挑选?里边只要SPC560D40的选项

- 上一篇: 奥迪A5-太平洋汽车

- 下一篇:高低压断路器的分类与选择999纯干货建议收藏!